華為Mate 60 Pro搭載的麒麟9000S處理器將公眾視線聚焦到了國產芯片製造之上。

跑分軟件讀取的數據、第三方拆解報告等諸多線索交叉顯示,麒麟9000S是一顆7nm工藝芯片,它的產地清楚的標註這中國大陸,然而專用於生產7nm芯片的EUV早就於2019年對中國出口管制,中國的芯片代工企業只能獲取到193nm光源的DUV光刻機,且這個出口管制的口子仍在不斷收緊。日前,荷蘭光刻機製造商ASML確認,到2024年將無法向中國客戶交付DUV光刻機。

問題來了,這顆7nm芯片是如何生產出來的?

7nm工藝麒麟9000S的出現,大致有兩種可能,一種是國產EUV光刻機實現突破,另一種是芯片製造商在DUV上,採用了特殊「魔法」,變相生產出了7nm工藝芯片。

從客觀情況來看,後一種推測的可能性,要遠遠大於前一種,這一點在《中國芯片,只缺光刻機?》這篇文章中我也提到過,我們不單純是缺光刻機,也包括它的配套,基礎研究等突破,且即便EUV光刻機完成研發,到用於商用芯片的大規模量產,這個過程也不是一兩年就能完成的事情。

所以本篇文章,我們將着重聚焦講解用來生產28nm芯片DUV光刻機,為什麼能夠生產7nm芯片?以及順便聊一聊為什麼又說7nm,28nm這些工藝節點的命名是一個文字遊戲。為了幫助大家理解,我們先從鋪墊一下芯片製造相關的知識點,包括光刻原理、光刻流程。

01 重識光刻

用193nm的DUV(深紫外)光刻機,覆蓋的是28nm及以上工藝節點,用DUV製造7nm工藝的芯片,這聽起來是不可能完成的任務,因為商用的DUV光刻機光源的最短波長為193nm,與7nm有28倍的差距,看似無法突破,但業界確實用DUV製造出了7nm芯片,這是怎麼實現的呢?

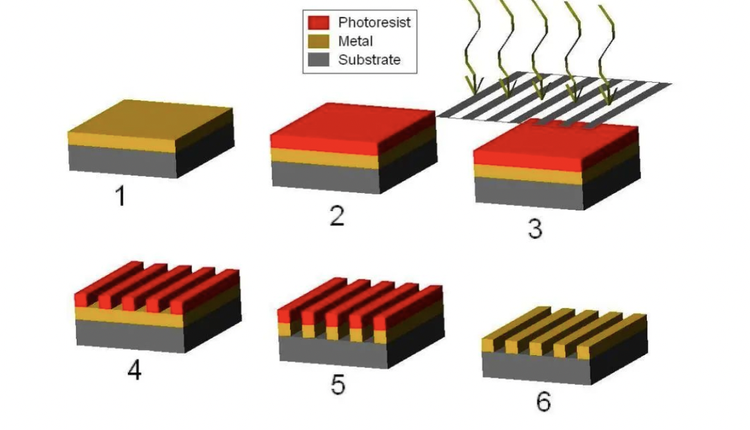

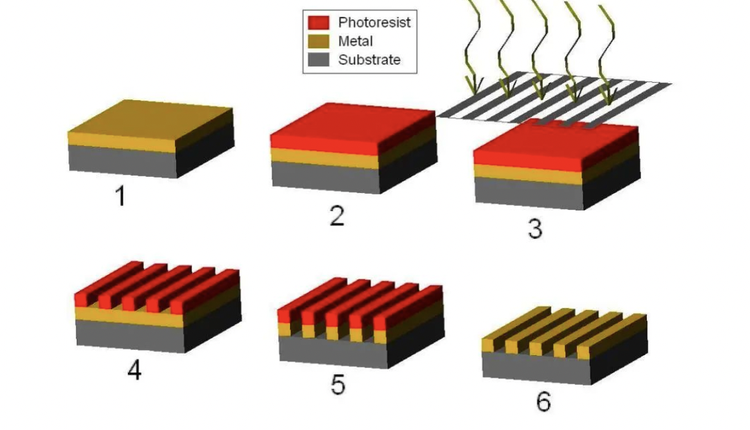

首先簡要介紹一下光刻機的原理和芯片生產的光刻流程。光刻的原理跟傳統膠片電影放映有點相似,放映電影是把圖案從電影膠片透射到銀幕上,而光刻則是將圖案從掩膜版透射到晶圓表面,從而在晶圓表面上加工出特定的圖案和線條(如上圖)。

具體來說,首先是製作光刻所需的掩膜版,這相當於膠片。這需要將芯片版圖用金屬鉻刻蝕到一種特殊的玻璃上,做出掩膜版。然後用紫外光透過掩膜版照射到下方的晶圓上。

掩膜版上的圖案(也就是鍍鉻的部分)遮擋了一部分光線,而沒有被遮擋的圖案可以將光線透過去,這樣電路圖案就轉移到了晶圓表面。而晶圓表面預先塗覆了光刻膠,被照射到的光刻膠發生化學反應,被化學溶液腐蝕清洗掉,露出了下方的晶圓,能被後續的工序刻蝕掉,從而在晶圓上加工出對應的圖案和線條。

這樣就可以一層一層加工出晶體管、金屬互連線等芯片結構。

為了加工更小尺寸的晶體管,需要縮短紫外光的波長,這樣照射在光刻膠上加工出來的線條才會更精細。

早期的紫外光的波長為436nm的g線,能加工工藝尺寸500nm以上的晶體管。隨着晶體管尺寸繼續縮小,光刻機上的紫外光源的波長縮短到了405nm的g線和365nm的i線。當晶體管工藝尺寸縮小到了250nm以下,對應需要紫外光源的波長縮短到248nm和193nm,也就是深紫外光(DUV)的範圍。

02 「7nm」的文字遊戲

其次要和大家強調一下,芯片製造商工藝節點的概念,也就是7nm、14nm、28nm等等,是晶圓製造廠為了標識芯片加工技術所起的一個名字或者規格。

20世紀90年代中後期,工藝節點是芯片廠能實現的晶體管柵極最小長度(線寬),簡稱柵長。但是現在的7nm工藝節點不真正等於數學上的7nm,在7nm工藝芯片上的每個晶體管尺寸都遠大於7nm,「7nm」只是一個「標籤」。

7nm之所淪為一個標籤,離不開20世紀90年代以來半導體製造商制定的命名規範。

按照摩爾定律和登納德縮小規則,每過一代柵長就縮小為上一代的70%,如果上一代晶體管的柵長是1微米,那麼下一代是0.7微米,這樣每個晶體管的面積剛好減半,或者讓元件數量翻倍。

到了2005年,半導體製造廠發現,柵長無法按照每代減小為70%的節奏繼續縮短,因為柵長越短,漏電流就越大,芯片過熱問題就越嚴重。可是業界已經習慣了每次升級就乘以0.7的做法,於是半導體製造商不管下一代的柵長是否能縮小為70%,就直接將上一代工藝節點乘以0.7作為新的工藝節點,所以我們有了32nm、22nm、14nm、10nm、7nm等工藝節點名稱。

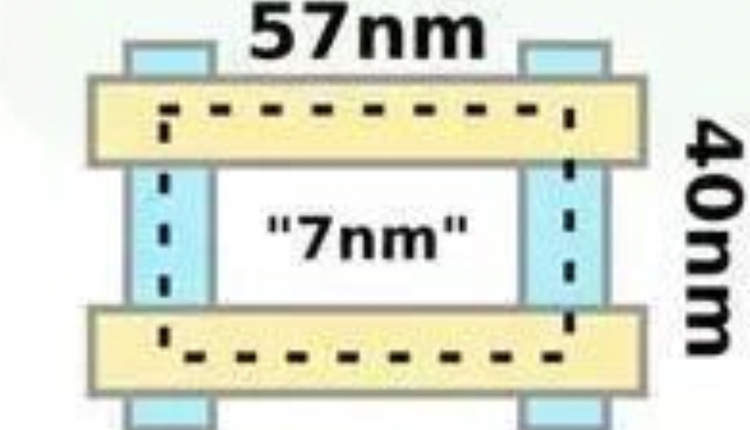

既然工藝節點無法真實地反映晶體管尺寸,那麼業界用什麼尺寸來表示晶體管大小呢?實際上,業界會用工藝柵間距(CPP)和金屬間距(MMP)用兩個尺寸來共同表示(如上圖),它們相當於一個長方形的長和寬,二者的乘積決定了晶體管的面積。例如,台積電的7nm工藝柵間距(CPP)等於57nm,金屬間距(MMP)是40nm。三星也差不多,這兩個數據分別是54nm和36nm,都遠遠大於半導體製造廠所標稱的7nm。

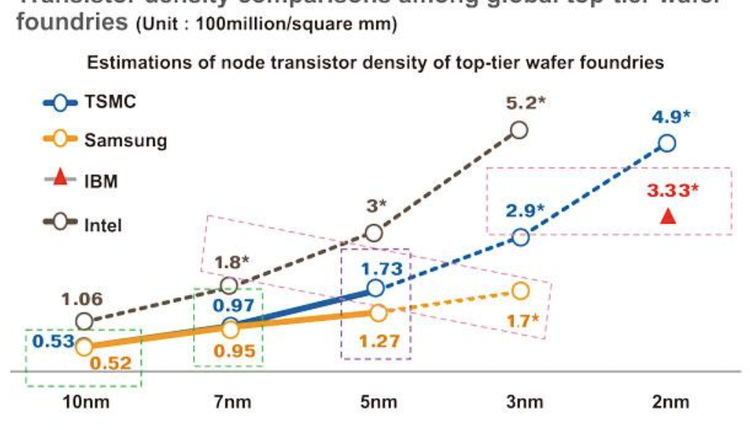

主要芯片製造商在不同節點上,對應的晶體管密度,英特爾、台積電和三星10nm節點,對應每平方毫米上的晶體管數量分別為106萬、53萬和52萬。

過去英特爾比較實在,習慣用溝道長度(比柵長小)來定義節點,有說法是為了緊扣摩爾定律,不論原因如何,命名上總比競爭對手們吃虧。

比如,英特爾的10nm,晶體管密度比台積電和三星的7nm還要多(如上圖),但從營銷的邏輯來說,別人都說7nm,英特爾說自己是10nm,吃了個「沒文化」的虧,所以後來英特爾也跟着對手們,改用intel 4、intel 3這樣的節點命名方式。

上面闡釋的這些,只是想告訴你,節點的命名,就是一個文字遊戲,7nm工藝對應的最小金屬間距在36nm-40nm左右。

有了這個認知,我們就可以來講講前面提到的193nm DUV光刻機,和要製造的7nm芯片之間的關係。或者這樣說,DUV生產7nm芯片,實際上是利用193nm光源的光刻機,生產金屬間距36nm-40nm的芯片。

193nm光源,和36nm的金屬間距中間,差5倍左右,如何跨越這個差距?這裡就不得不提DUV乾式光刻機到DUV浸沒式光刻機的迭代了。

DUV光刻機的光源波長雖然為193nm,但是光在水中會發生折射,波長則會縮短。193nm的紫外光在水中的折射率為1.44,波長為134nm。根據這一原理,林本堅在1987年提出了浸沒式光刻,即在晶圓表面和透鏡之間增加一層超純水,讓紫外光折射,從而將波長降低為134nm,2003年荷蘭的ASML基於這項研究,第一個實現了浸沒式光刻機。

從DUV乾式光刻機到DUV浸沒式光刻機,從193nm光源波長到134nm波長的紫外光,這與36nm的金屬間距的差距再度縮小至4倍。

03 多重曝光搞定「最後一公里」

浸沒式光刻機的出現,再次縮小了和「7nm」工藝的差距,但行業仍無法直接用這種光刻機加工出大家口中的「7nm」芯片,如果芯片製造商真要製造傳聞的7nm麒麟9000S,雙重曝光和多重曝光必不可少。

為了解釋雙重曝光技術,讓我們舉一個照相的例子。假設你是一個攝影師,要拍攝一幅運動會隊列的照片,這個隊列只有20個人,按照2米的間距站開,顯得非常稀疏,怎麼拍出40個人的感覺?你有一種解決方案,先拍完第一張,然後再讓每個人平移1米,拍出另一張,隨後通過軟件,將兩張照片合成在一起。

雙重曝光技術也可以如法炮製。使用一組掩膜版,加工出間隔134nm的線條,再使用另外一組掩膜版,平移一段距離加工出另外一組間隔134nm的線條,二者組合起來,就有了間隔67nm的線條,這距離36nm又前進了一步。從22/20nm開始,業界開始導入雙重曝光技術。

為了實現雙重曝光技術,業界開發出了LELE法(光刻-刻蝕-光刻-刻蝕),它需要塗兩次光刻膠,曝光兩次,第一次曝光在硬掩膜上複製圖形,第二次曝光在光刻膠上複製出最小線寬圖案。但是由於使用兩次曝光設備,大大推高了製造成本,花費的時間也更久。要知道光刻占整個製造時間的50%左右,增加一倍的曝光會大大延長整個製造時間。

為此,業界又開發出了效率更高的自對準雙重圖形化法(SAPD),這種方法將兩次塗光刻膠減少到了一次,它利用化學氣相沉積(CVD)技術將氧化硅沉積在第一次塗的光刻膠周圍,自然地形成了對準後的加工位置,從而能實現第二次圖形加工。

有了這些技術,雙重曝光就能加工出67nm的金屬間距,不過這距離36nm還差了兩倍,怎麼去突破最後的這2倍的差距?

有一個簡單粗暴的方法,就是再做一次雙重曝光,總共做四重曝光,就能再一次將67nm減半,加工出最小34nm的線條,剛好符合加工7nm所需的36nm的金屬間距。

不過這個方法要付出的代價實在太大了,曝光時間是單重曝光的4倍,需要製備更多的掩膜版,每次曝光都需要更多的配套工序(光刻膠塗覆、軟烘烤、對準、顯影、甩干、硬烘烤、圖形檢測等),所需的全部製造工序從幾百道增加到上千道,大大增大了製造的時間成本和物力成本。此外,曝光時間的增加會使鏡頭髮熱增大,溫度升高又會導致鏡頭光路變形,套刻精度更難以控制,與之匹配的薄膜和刻蝕工藝難度也大大增加。還有,以上的計算沒有考慮數值孔徑(NA)對光刻精度的影響(這部分不涉及多重曝光的理解,故本文不對套刻精度、數值孔徑詳細展開)。為了提高數值孔徑,還需要把鏡頭做得更大。

基於多重曝光技術,台積電於2016年6月開始用DUV生產7nm芯片(N7),三星則於2018年開始用DUV量產7nm芯片(7LPP)。至此,用DUV實現7nm工藝才成為現實。

一句話總結,雖然可以通過多重曝光的手段,利用193nm光源的DUV,生產7nm芯片,但時間、材料、人力成本都會大大增加,且由於工序極大的增加,良率也會受到影響。

作為對比,EUV的波長只有13.5nm,一次曝光就能做出7nm芯片,只不過EUV吊足了晶圓廠的胃口,直到2020年才正式在5nm工藝上使用。在此之前GlobalFoundry失去了耐心,宣布由於高昂的成本停止7nm技術的開發。

04 DUV能突破5nm工藝嗎?

不過,這還不是故事的全部。

除了多重曝光技術,用DUV加工7nm工藝還需要很多技術的配合才能實現,包括相位移模板(PSM)、離軸光照、光學臨近校正(OPC)、優化光圈和光刻圖形(SMO)等,這幾項技術催生了一門新的子學科:計算光刻。它所需的龐大數據使得英偉達的GPU芯片也成為了計算所需的工具,其推出cuLitho軟件加速庫,宣稱可以將計算光刻的用時提速40倍。

之所以需要計算光刻,是因為當掩膜版上的線條變得很小時,紫外光通過掩膜版時會產生偏差,讓光刻圖形畸變。為此研究人員想到了一個方法,預先計算出掩膜版上可能的畸變,從而逆向地設計光刻所需的掩膜版的最佳形狀,提前抵消這些畸變,這叫做逆向光刻計算,而這需要非常龐大的計算量,普通的計算機根本無力承擔,研究人員不得不使用超級計算機和雲計算。

與此同時,研究人員又將人工智能的機器學習算法應用到計算光刻上來。新一代的卷積人工神經網絡被應用於光刻工藝模型、掩模優化、SEM數據處理等方面,而訓練數據又需要龐大的GPU芯片組。除了器件層面的優化,研究人員甚至還將電路設計中要考慮的因素也融入到器件製造中來,在電路設計階段就考慮對製造和光刻的影響,這叫做DTCO(設計與工藝技術協同優化),而這又需要EDA廠商升級算法和軟件。

可以說,為了讓DUV能製造出7nm工藝芯片,業界已經無所不用其極。下一步如果繼續採用DUV製造5nm工藝芯片,四重曝光也不夠了,需要6-8重曝光,以及更多的掩膜版,更長的光刻時間,更高的物力成本,這已成為不堪忍受之重。所以5nm芯片出來時,剛好EUV光刻機也準備好了,才將業界從繁瑣的多重曝光下解脫出來,而7nm工藝也成為目前業界使用DUV製造出來的最後一代工藝。

關於作者:

《芯片簡史》 作者:汪波 2023出版 ,*作者汪波博士是芯片研究專家,科普作家,在華為公司、法國里昂納米國家實驗室和北京大學深圳研究生院有二十多年的研究和教學經驗,著有《芯片簡史》、《時間之問》和《時間之問·少年版》,其中《芯片簡史》入選2023年「南國書香節」十大好書榜,探照燈好書、第三期「新發現·科普書單」、百道網2023上半年影響力圖書、中國傳媒出版商報2023二季度影響力書單。

(全文轉自36氪,原文已被刪除)

本文由看新聞網轉載發布,僅代表原作者或原平台觀點,不代表本網站立場。 看新聞網僅提供信息發布平台,文章或有適當刪改。

本文網址:https://vct.news/zh-hant/news/ed3842f0-7f8b-4f69-8576-2f7c1f0f3543

評論被關閉。